The APECS pilot line at a glance:

As part of the EU Chips Act the APECS pilot line marks a major leap forward in strengthening Europe’s semiconductor manufacturing capabilities and chiplet innovation. By providing large industry players, SMEs, and start-ups with easier access to cutting-edge technology, the APECS pilot line will build a strong foundation for resilient and robust European semiconductor supply chains.

Within APECS, the institutes collaborating within the Research Fab Microelectronics Germany (FMD) are working closely with other European partners, making a significant contribution to the European Union´s goals of increasing technological resilience, strengthening cross-border collaboration and enhancing its global competitiveness in the semiconductor technologies.

APECS is the novel pan-European pilot line to establish a groundbreaking infrastructure for heterogeneous integration and advanced packaging

Europe's investment in semiconductor research, through strategic projects such as APECS in the EU Chips Act, is crucial to reduce our dependence on international supply chains that are heavily concentrated in other regions. By boosting technological sovereignty, APECS is securing Europe's long-term economic stability and positioning the EU as an indispensable partner in the technological breakthroughs that lie ahead for the digital age. Furthermore, APECS will play a pivotal role in Europe's transition towards a carbon-neutral and circular economy through its promotion on eco-design and green manufacturing initiatives.

APECS will be a key driver of collaboration among European RTOs, industry and academia, fostering a lively innovation ecosystem. Customers will benefit from a single point of contact to the APECS pilot line. APECS covers end-to-end design and pilot production capabilities, to accelerate progress from cutting-edge research to practical, scalable manufacturing solutions.

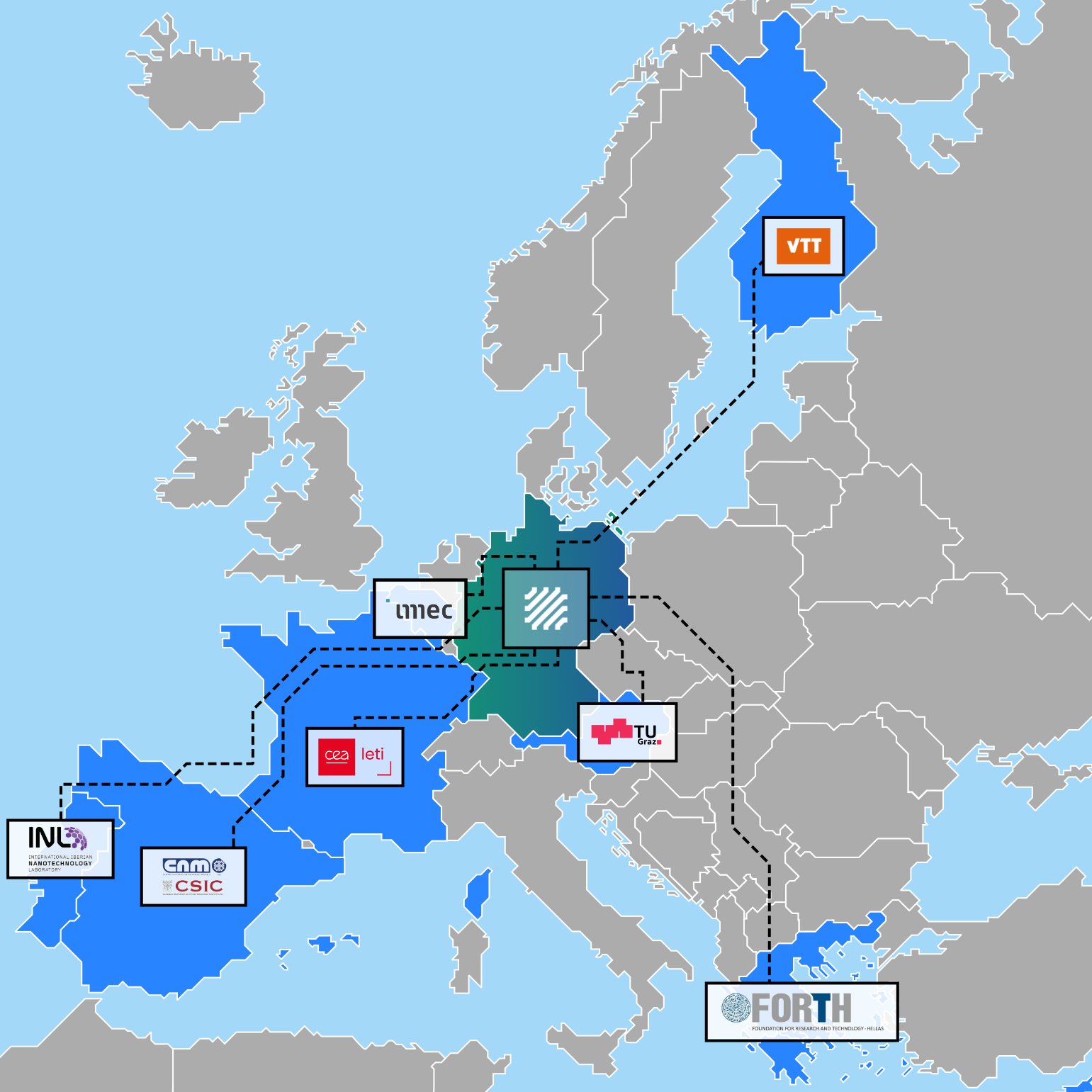

The APECS consortium brings together the technological competences, infrastructure, and know-how of ten partners from eight European countries: Germany (Fraunhofer-Gesellschaft as coordinator, FBH, IHP), France (CEA-Leti), Belgium (imec), Finland (VTT), Austria (TU Graz), Greece (FORTH), Spain (IMB-CNM, CSIC) and Portugal (INL).

Center for Advanced CMOS & Heterointegration Saxony

Center for Advanced CMOS & Heterointegration Saxony